In questa pagina continua l'analisi del modulo MSSP in modalità Master SPI del PIC18. In particolare è descritto come utilizzare le interruzioni e come rendere più flessibile la scelta della frequenza del clock SPI. Per proseguire è utile conoscere quanto descritto in PIC18 come master SPI.

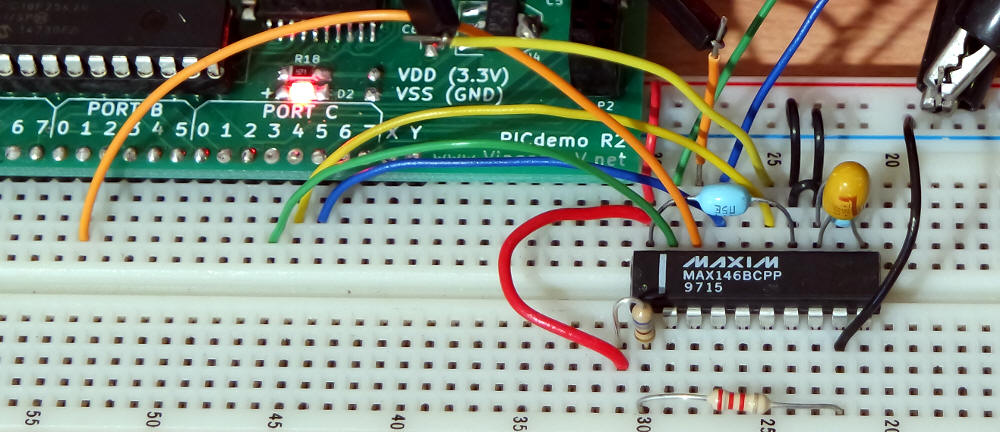

Il circuito utilizzato è stato realizzato su breadboard con un PIC18F25K20 ed un ADC a 12 bit MAX 146; è descritto in questa pagina e mostrato nella fotografia di apertura.

In questa pagina non è spiegato cosa è e come si usa il bus SPI. Se serve, qui trovate qualche informazione.

Osservando il codice che utilizza il modulo hardware MSSP descritto in questa pagina, si nota la presenza di codice "bloccante", cioè di un loop di attesa del termine di una operazione di una periferica, nel caso specifico la trasmissione di un byte da parte del modulo MSSP:

while (!SSPSTATbits.BF); // SSPBUF is empty?

L'aspetto negativo è, da una parte, la perdita di tempo attendendo il completamento di un'operazione hardware, dall'altra l'impossibilità di eseguire altro codice "contemporaneamente".

Nel caso specifico del bus SPI in configurazione master, questo problema potrebbe essere relativamente marginale in quanto il tempo necessario alla trasmissione di un byte è:

Nel caso di SPI Master le soluzioni che utilizzano le interruzioni hanno quindi spesso solo di interesse "accademico" in quanto in genere l'overhead dovuto alle interrupt è tale da rendere trascurabili se non nulli i vantaggi. Ma in determinati contesti potrebbe essere utile utilizzare questa tecnica:

A fondo pagina il codice di esempio, dove è mostrato lo scambio di un blocco di 17 byte tra un PIC18 e l'ADC MAX146. Per la comprensione del funzionamento di MAX146 secondo la modalità qui utilizzata, si legga quanto presentato in questa pagina.

Le particolarità del codice sono relative alle impostazioni delle interruzioni, peraltro assolutamente convenzionali:

La ISR viene invocata quando la trasmissione di un byte termina. Le operazioni che deve effettuare:

Queste operazioni devono essere svolte fino alla trasmissione dell'intero buffer di trasmissione, 17 volte in questo esempio.

Il diagramma temporale corrispondente:

Dall'alto:

La situazione mostrata può essere considerata prossima al limite massimo per l'uso di SPI interrupt-driven: infatti un aumento della frequenza del bus SPI (o una diminuzione del clock del processore) ridurrebbe ulteriormente il tempo disponibile all'esecuzione del codice al di fuori della ISR, rendendo di fatto non praticabile questa scelta. In definitiva: si tratta di una limitazione architetturale di questa versione del PIC18. Osservazione 1.

A fondo pagina è presente un esempio che può essere considerato lo scheletro generico del codice lato Master per scambiare un frame di lunghezza fissa con uno Slave. Il frame ha contenuto qualsiasi (anche se nell'esempio è la stringa "MASTER 4 #", dove 4 è una cifra comprese tra 0 e 9, incrementata ad ogni trasmissione). Questo codice è quello utilizzato con l'omologo programma slave.

L'analisi del codice è lasciata come esercizio.

La scelta del clock SPI è rigidamente legata a quella del processore attraverso un divisore a tre soli livelli (/4, /16 e /64). A volte questa scelta è oltremodo limitante. Per esempio il bus SPI di MAX 146 permette di arrivare fino a 2 MHz rendendo non solo più rapido il trasferimento dei dati, ma anche la conversione AD.

Il secondo codice che trovate a fondo pagina permette di scegliere con maggiore "elasticità" la frequenza di SPI, utilizzando l'uscita di Timer2 come sorgente di clock SPI. La modalità di funzionamento di MAX 146, come nel precedente esempio, è identica a quanto qui descritto.

Le particolarità del codice sono relative alla scelta delle impostazioni di Timer2 per generare la frequenza desiderata (2 MHz, in questo caso):

L'unica avvertenza è relativa al numero di divisori che riducono il clock del processore, ben tre:

Quindi complessivamente, in questo esempio: 64 MHz / 4 / 4 / 2 = 2 MHz.

Il diagramma temporale corrispondente:

Dall'alto:

Eventuali aumenti della frequenza del clock SPI, fino a 16 MHz, renderebbe il throughput maggiore, anche se non proporzionalmente: il tempo utilizzato per le elaborazioni software rimarrebbe infatti invariato.

Data di creazione di questa pagina: luglio 2015

Ultima modifica: 27 dicembre 2015

PIC18 in C - Versione 0.991 - luglio 2019

Copyright 2014-2019, Vincenzo Villa (https://www.vincenzov.net)

PIC18 in C di Vincenzo Villa è distribuito con Licenza Creative Commons Attribuzione 4.0 Internazionale